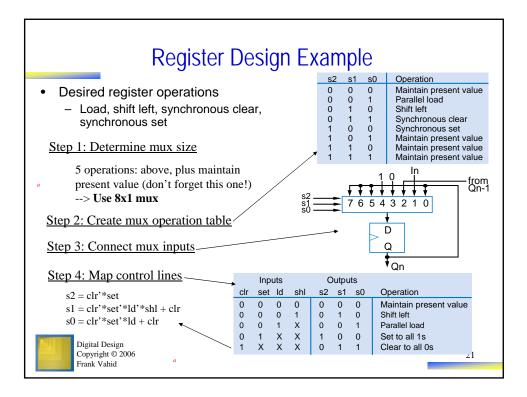

|     | design reg<br>-step proces    | ister with desired operations using simple<br>ss                                                                                                                                                 | Ð |

|-----|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

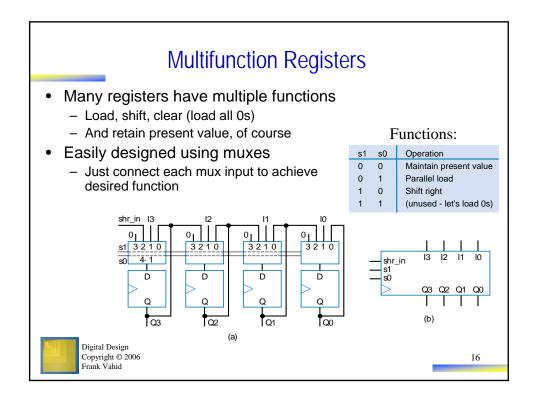

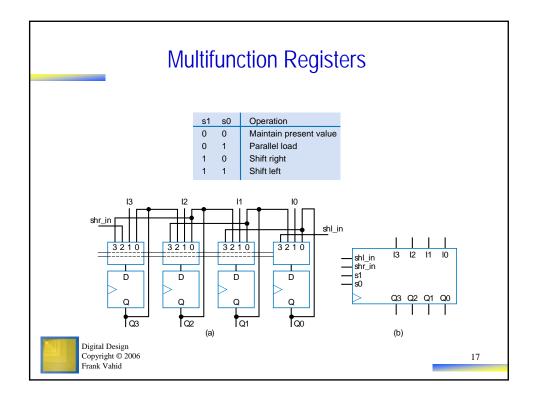

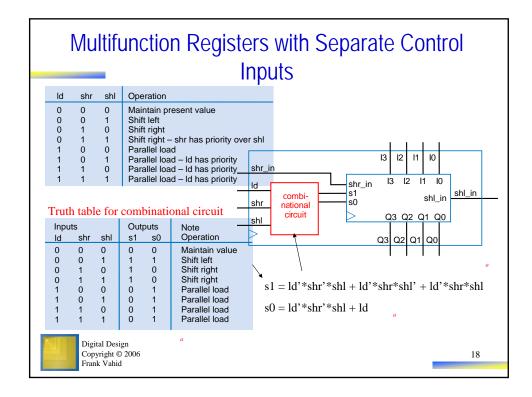

| TAB | LE 4.1 Four-step pro          | cess for designing a multifunction register. Description                                                                                                                                         |   |

| 1.  |                               | Count the number of operations (don't forget the maintain present value operation!) and add in front of each flip-flop a mux with at least that number of inputs.                                |   |

| 2.  | Create mux<br>operation table | Create an operation table defining the desired operation for each possible value of the mux select lines.                                                                                        |   |

| 3.  | Connect mux<br>inputs         | For each operation, connect the corresponding mux data input to the<br>appropriate external input or flip-flop output (possibly passing through<br>some logic) to achieve the desired operation. |   |

| 4.  | Map control<br>lines          | Create a truth table that maps external control lines to the internal mux<br>select lines, with appropriate priorities, and then design the logic to<br>achieve that mapping                     |   |

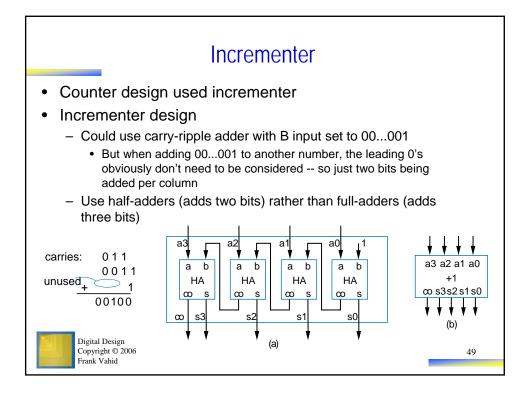

| Can build faster incrementer                          |        |        | Outputs |        |        |        |        |        |        |

|-------------------------------------------------------|--------|--------|---------|--------|--------|--------|--------|--------|--------|

|                                                       | a3     | a2     | a1      | a0     | c0     | s3     | s2     | s1     | s0     |

| using combinational logic                             | 0      | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 1      |

| design process                                        | 0      | 0<br>0 | 0<br>1  | 1<br>0 | 0      | 0<br>0 | 0<br>0 | 1<br>1 | 0<br>1 |

| <ul> <li>Capture truth table</li> </ul>               | 0      | 0      | 1       | 1      | 0      | 0      | 1      | 0      | 0      |

| •                                                     | 0      | 1      | 0       | 0      | 0      | 0      | 1      | 0      | 1      |

| <ul> <li>Derive equation for each output</li> </ul>   | 0      | 1      | 0       | 1      | 0      | 0      | 1      | 1      | 0      |

| • c0 = a3a2a1a0                                       | 0      | 1      | 1       | 0      | 0      | 0      | 1      | 1      | 1      |

| •                                                     | 0      | 1<br>0 | 1<br>0  | 1<br>0 | 0<br>0 | 1<br>1 | 0<br>0 | 0<br>0 | 0<br>1 |

| • s0 = a0'                                            | 1      | 0      | 0       | 1      | 0      | 1      | 0      | 1      | 0      |

| <ul> <li>Results in small and fast circuit</li> </ul> | 1      | 0      | 1       | 0      | 0      | 1      | 0      | 1      | 1      |

|                                                       | 1      | 0      | 1       | 1      | 0      | 1      | 1      | 0      | 0      |

| <ul> <li>Note: works for small N larger</li> </ul>    | 1<br>1 | 1<br>1 | 0<br>0  | 0<br>1 | 0<br>0 | 1<br>1 | 1<br>1 | 0<br>1 | 1<br>0 |

| N leads to exponential growth,                        | 1      | 1      | 1       | 0      | 0      | 1      | 1      | 1      | 1      |

| like for N-bit adder                                  | 1      | 1      | 1       | 1      | 1      | 0      | 0      | 0      | 0      |

| like for N-bit adder                                  |        | •      | •       | Ũ      | -      | •      | •      | •      | •      |

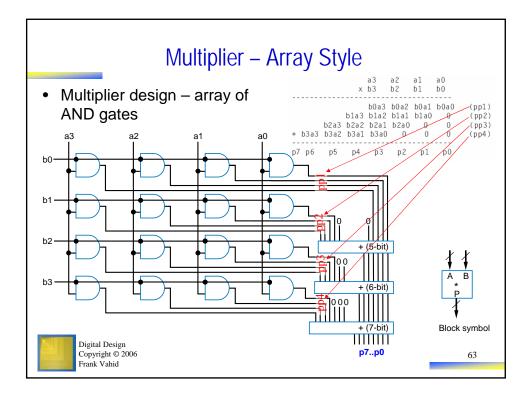

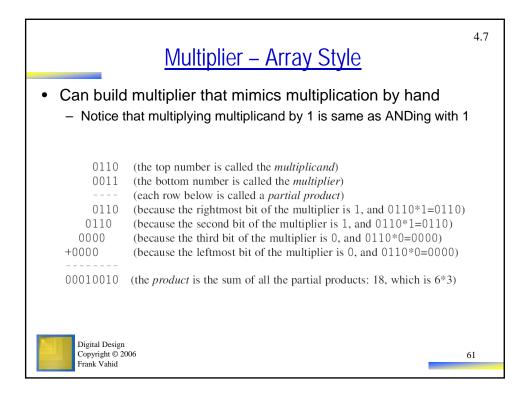

| Gener | alized r | epres | senta                      | tion (       | of mu    | iltiplic  | cation   | by hand                          |  |

|-------|----------|-------|----------------------------|--------------|----------|-----------|----------|----------------------------------|--|

|       |          |       | Х                          |              | a2<br>b2 | a1<br>b1  | a0<br>b0 |                                  |  |

|       | + b3a3   |       | b1a3<br>a3 b2a2<br>a2 b3a1 | b1a2<br>b2a1 | b2a0     | b1a0<br>0 | 0        | (pp1)<br>(pp2)<br>(pp3)<br>(pp4) |  |

|       | p7 p6    | р5    | р4                         | р3           | p2       | p1        | p0       |                                  |  |