# DIGITAL COMPUTER DESIGN

Logic, Circuitry, and Synthesis

## **EDWARD L. BRAUN**

Aerospace Corporation

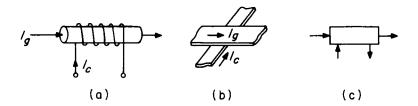

Los Angeles, California

1963

ACADEMIC PRESS . NEW YORK AND LONDON

COPYRIGHT © 1963, BY ACADEMIC PRESS INC.

ALL RIGHTS RESERVED.

NO PART OF THIS BOOK MAY BE REPRODUCED IN ANY FORM,

BY PHOTOSTAT, MICROFILM, OR ANY OTHER MEANS, WITHOUT

WRITTEN PERMISSION FROM THE PUBLISHERS.

ACADEMIC PRESS INC. 111 Fifth Avenue, New York, New York 10003

United Kingdom Edition published by ACADEMIC PRESS INC. (LONDON) LTD. Berkeley Square House, London W.1

LIBRARY OF CONGRESS CATALOG CARD NUMBER: 63-15725

First Printing, 1963 Second Printing, 1967

PRINTED IN THE UNITED STATES OF AMERICA

#### Preface

This book provides an introductory treatment of the logical structure, electronic realization, and application of digital information processors. The extent of coverage of each major topic should also make the book useful as a review and reference text for persons experienced in the field. Each major chapter is a relatively self-contained unit in an important area: Boolean algebra for switching networks (Chapter 3), electronic building blocks for switching circuits (Chapter 4), memories for digital computers (Chapter 5), arithmetic operations in digital computers (Chapter 6), system design of GP (integral transfer) computers (Chapter 7), an extensive description of DDA (incremental transfer) computers (Chapter 8), and detection and correction of errors (Chapter 9), and input-output equipment (the Appendix).

With the exception of Chapters 4 and 5, the presentation is on a functional level, i.e., in terms of how elements with defined input-output characteristics may be organized to synthesize subsystems or systems with specified functional capabilities. Although functional descriptions and circuit problems cannot be separated completely, the discussion of detailed problems in the electronic realization of computers has been confined mainly to these two chapters. This was done for a number of reasons-first of all, in order not to obscure (by the intricacies and details of practical means of mechanization) the conceptual simplicity of fundamental principles treated in other chapters. This separation and the way material is organized in each chapter also facilitates looking-up particular topics. Also, while the entire field is evolving rapidly, developments in circuit techniques have advanced more rapidly than in logical design. When the writing of this book was begun, the clock-repetition rate of most digital computers was about 100 kc. Currently (1962) computer circuits are under development for operation in the microwave region of several hundred megacycles. (Developments in microwave, tunnel diode, and superconductive circuits are described in Chapters 4 and 5 and also referenced in the bibliographies of these chapters.)

The importance of digital information processing technology in the betterment of human welfare, in government, commerce, industry, science, viii PREFACE

engineering, and military systems (as well as dangers inherent in misuse) makes it desirable that certain principles and the breadth of applications be widely appreciated. The text's emphasis on the functional approach makes much of the subject accessible to those with limited technical backgrounds. The presentation of material is designed to supplement instruction in university level classes and also to facilitate independent study. Because problems associated with various types of electronic circuits are largely confined to two chapters, the intelligent reader with limited knowledge in electrical and electronic circuits can (in accordance with his capability and inclinations) skim these chapters and still understand and benefit from the remainder of the text. (An additional reservation is that appreciation of all of Chapter 8 calls for a basic knowledge of ordinary differential equations.) The entire text can be understood by one having a background equivalent to a Bachelor's degree in electrical engineering with mathematics through differential equations.

Even after thorough study of branches of a subject, one may still have doubts on how to apply this knowledge in the synthesis of a particular design. Often this situation can be alleviated by the study of examples that illustrate in detail the application of the basic material. In the present case an effort was made to integrate material presented in earlier chapters by presenting (in Chapter 7) a detailed explanation of two simple digital computer logical designs.

The author is indebted to many organizations and individuals who have advanced the digital computer field and whose work forms the reservoir from which the material for this book was drawn. Many of these sources are listed in the bibliographies. Reports and publications of the Massachusetts Institute of Technology, John von Neumann and his colleagues at the Princeton Institute for Advanced Study, the University of Illinois, and the University of Manchester deserve special mention. If the principal source of any important material has not been properly referenced, the author invites this being called to his attention.

The author is grateful to the Northrop Corp. and Dr. Erik Ackerlind for the opportunity to enter the digital computer field. Thanks are due Lockheed Aircraft Corp., Hughes Aircraft Co., and Information Systems, Inc., for furnishing typing assistance, Mrs. Barbara Fine for typing the final manuscript, and the Aerospace Corp. for assistance on the subject index. Acknowledgment is due Mr. Geoffrey Post for his encouragement while the author was at Information Systems, Inc.

It is a pleasure to acknowledge valuable aid from the following individuals, who read and constructively criticized final page proofs: Chapter 3, William Shooman, System Development Corp.; Chapter 4 (transistor

PREFACE ix

circuits) and Chapter 5 (magnetic surface recording techniques), Marvin G. Ettinghoff, Librascope, Inc.; Chapter 5 (magnetic core memories), Milton Rosenberg, Electronic Memories, Inc.; Chapter 6, Dr. John M. Salzer, Space Technology Laboratories.

The list of acknowledgments would be incomplete without mention of my family's understanding and forbearance during the period of preparation of this book.

EDWARD LOUIS BRAUN

March 1963

# 1. Introduction

#### 1.1. Uses of Number

The subject matter of this book is the stored program digital computer. We will consider its fundamental nature, ways of describing its logical organization, various means of mechanization, and principles and techniques useful in its synthesis and utilization. Since these machines accomplish their function by means of operations on numerically coded information, some preliminary discussion is in order on the subject of numbers. We will consider briefly the nature of numbers, certain symbols and notations used to represent them, and a description of mechanical and/or electronic means for representing numbers and operating on them.

Numerical symbols may be used for various purposes. Sometimes they are used merely as labels to distinguish one of a set of objects from the others. In other words, they can be used as names or symbols for objects. They are convenient to use as names of persons or things because they provide an inexhaustible supply of such names.

Ordinarily, one associates a definite order among numerals (or groups of numerals). Often, numerals are used for this characteristic alone, as in assigning them to houses on a street. The function of a street address is not to indicate how many houses there are on a street, but to indicate a particular house's position relative to other houses on the street, i.e., its order. The use of numerals to indicate the number of items in a set will be discussed in Section 1.2.

#### 1.2. Counting

Before considering how numbers came to be associated with the process of counting, it is well to emphasize the distinction between ordinal and cardinal numbers since, in common usage, the word number alone may refer to either. When numbers are used solely for an order property that has been defined previously for them, they are called ordinal numbers (or ordinals)—for example, numbers indicating relative locations or points in time. Numbers used to designate the manyness of a set of things are called cardinal numbers (or cardinals). As mentioned in Section 1.1, numerals can be used merely as convenient tags or symbols to distinguish objects from one another. In this case, the numerals are used neither to

convey the property of ordinality nor cardinality. Within a computer, numbers may be used in any of these ways. An important property of all numerical symbols is that mathematical and logical operations can be performed on them to serve various useful purposes.

A fundamental numerical operation is that of determining whether the number of elements in one set is equal to, greater than or less than the number of elements in another set. An obvious procedure is to pair off an element in one set with an element of the other set, at the same time removing each element from its set, and to continue this process until one or the other set is depleted. For this process to be generally useful for enumerating elements in a set, it is necessary that one have available a standard set of sets. The smallest of these subsets will contain only one element, and the entire set of subsets may be built up from it simply by the addition of one element at a time. The idea of using a standard set of sets, formed from some easily transportable objects, resulted in a great convenience since it meant that one could determine the relative magnitude of two sets of objects and, also, the number of elements in each set without bringing the sets in proximity. Since each subset is included in the next larger subset of the set, the total number of elements to be provided did not have to exceed the largest set which might have to be enumerated. The most convenient set of elements at primitive man's disposal was the set comprised of his fingers (and toes), and it was only natural for him to use them (therein lies the origin of the quinary, bi-quinary and decimal number systems). As the need to enumerate larger sets developed, sets of small pebbles or beads (also easily transportable) came into use. At a later time, a symbol (or group of symbols) was assigned to each subset of the set. Then, the manyness of sets could be indicated conveniently in terms of these symbols. Finally, this led to the process of ordering the symbols in accordance with the manyness of the sets they represented, and to our present day convention in which we count by introducing the name of the symbol for the next larger set in a standard sequence each time the present set is augmented by "1." This same type of procedure allows us to count from any initially specified location in a sequence, to count backwards as well as forwards and, also, to count by multiple as well as single increments.

#### 1.3. Numerical Symbols

Early man represented a single element by a mark like | or —, both because of their similarity to an extended finger and because they were easy to inscribe with a stick or other pointed instrument. Two elements

were represented by | | or  $\equiv$ . From the former is seen the origin of the Roman numeral II. The latter when written quickly, without removing the instrument from the writing surface, would appear as Z, and is the origin of 2. Similarly  $\equiv$  becomes 3. The reasons for the choice of the other numerals are not so apparent, and need not be discussed here.

A major step forward in the representation of a collection of elements came with the use of special symbols to represent large collections of elements. For example, the Romans used V for five, X for ten, L for fifty, C for one hundred, D for five hundred, M for one thousand, etc. Even so, the representation of large numbers was cumbersome compared to present day notation. For example 3738 would be expressed as MMMDCCXXXVIII. Nevertheless, Roman numerals were retained in commercial accounting until the eighteenth century. One reason for their continued use was that they made addition and subtraction easier for those with little or no mathematical training. This was because they allowed these operations to be performed by a process more akin, on the surface, to counting than is addition (or subtraction) of modern numerals. Consider, for example, the addition of 854 to 3738

| 4592 | MMMMDLXXXXII  |

|------|---------------|

| 854  | DCCCL III     |

| 3738 | MMMDCCXXXVIII |

To obtain the sum in Roman numerals, one need only know that the sum of any number (from one through four) of the Roman numerals I, X, C, M, etc. was represented simply by writing each symbol in the sum a number of times equal to the frequency with which it appeared in the addends. The only other rules, which achieve a more compact notation, are that IIII + I = V, V + V = X, XXXX + X = L, L + L = C, CCCC + C = D, etc. Contrast this simple process of accumulating like symbols with modern decimal addition which requires memorization of the decimal addition table as well as knowing when sums or borrows are generated and their disposition.

### 1.4. Fundamentals of Computing Aids

The first significant mechanical aid to computing, the abacus, was invented in ancient times and is widely used in many parts of the world even today. It consists of an array of similar physical elements, each of which represents a count whose magnitude is determined by the row and column coordinates of the element's position. These physical elements are in the shape of beads, referred to by the Romans as calculi (the origin of the terms calculus, calculate, etc.). Each column is divided in

two by a crosspiece. There may be one or two beads above the crosspiece, and four or five below it. Each upper bead defines a count equal to that of five beads below the crosspiece in the same column. Both upper and lower beads within a column are free to move along the column. In the column on the extreme right each lower bead represents one. In the next column each lower bead represents ten. As one proceeds to the left, the value assigned to the beads in any column is ten times that assigned to the beads in the adjacent column on the right. A number is set into the abacus by pushing beads up to the crosspiece.

The abacus provided a speed advantage for addition or subtraction compared to the manipulation of written Roman numerals, due to the fact that beads could be moved about in less time than it took to write the operands and result in Roman numerals. Another reason for its use was that it provided a cheap means of temporary storage of information. Numbers could be readily inserted and erased simply by movement of the beads. Parchment and ink were not readily available, expensive, and therefore practical only for permanent records, documents, etc. Another cheap means of temporary storage that was used consisted of a board covered with a thin coat of wax. Marks could be scratched into the wax and erased by resmoothing the wax. However, this was a slow and tedious process. It was not until slates, blackboards, and paper came into common use just a few centuries ago that the abacus and similar devices known as counting boards were replaced in Europe.

In the abacus, an important concept appears whose significance was not appreciated until many centuries later. We refer to the idea of a positional notation, i.e., one where the value represented by a particular symbol is a function of where the symbol appears in a group. In the abacus, there is only one symbol, namely a bead, and these beads represent different magnitudes in accordance with their positions. The interpretation of a symbol according to its position is characteristic of modern numerical representation and one of its most important features. It makes it unnecessary to create new symbols for successively larger counts. With the positional notation, and its simple rule for going from one number to the next larger one, any new number, as large as we please, may be written from a basic small set of symbols. The number of symbols required to represent any magnitude depends on how many symbols are used in defining the basic set. In the decimal system, based on using the fingers for counting, ten symbols, the numerals 0, 1, 2, 3, ... 9 comprise the basic set and the representation of a number such as

$$d_i d_{i-1} d_{i-2} \ldots d_0 d_{-1} d_{-2} \ldots d_{-i}$$

is really the shorthand notation for

$$(d_i \times 10^i) + (d_{i-1} \times 10^{i-1}) + \ldots + (d_0 \times 10^0) + (d_{-1} \times 10^{-1}) + \ldots$$

where each d may represent any of the ten symbols: 0, 1, 2, 3, . . . 9. For example, the representation 2943.0 implies:  $(2 \times 1000) + (9 \times 100) + (4 \times 10) + (3 \times 1) + (0 \times .1) = 2943.0$ . A system of numerical representation in which only two symbols are used is referred to as the binary system. A representation of a number in the binary system, such as

$$b_m b_{m-1} b_{m-2} \dots b_0 b_{-1} b_{-2} \dots b_{-n}$$

is the shorthand notation for

$$(b_n \times 2^n) + (b_{n-1} \times 2^{n-1}) + \ldots + (b_0 \times 2^0) + (b_1 \times 2^{-1}) + \ldots$$

where each b may represent either of the two symbols in the binary system: 0 or 1. Each of the symbols in a binary number is referred to as a bit (for binary digit). A comparison of the decimal and binary representations for numbers of magnitude from zero to ten is shown in Table 1.1. From it, a disadvantage of the binary system for written notation is apparent, namely the fact that the representation of a number requires, in general, more symbols than does the decimal system.

| Decimal    | Binary |

|------------|--------|

| 0          | 0      |

| 1          | 1      |

| 2          | 10     |

| 3          | 11     |

| 4          | 100    |

| 5          | 101    |

| 6          | 110    |

| 7          | 111    |

| 8          | 1000   |

| . <b>9</b> | 1001   |

| 10         | 1010   |

TABLE 1.1.

All mechanical, electromechanical, and electronic digital computing aids utilize the positional notation in the representation of numbers, for it allows a number of any magnitude to be formed from a defined, small set of symbols. This is of fundamental importance for the following reasons. First of all, it allows a digital unit to be fabricated from a relatively small number of standardized elements. Also, it is responsible for the high precision attainable, for the precision may be increased indefinitely simply by the use of more elements. For example, a common

mechanical method of representing a digit is by means of a notched wheel or disk which can be turned by a shaft through its center. At any time, the disk is defined to represent one of the symbols  $0, 1, 2, \ldots, 9$ , depending on the disk's angular displacement from an arbitrary reference. To represent a number with, say, n digits, n similar disks are used. To perform an addition, it is necessary to displace each disk by an amount proportional to the value of the digit to be added to the order defined by each disk. It is also necessary to intercouple the disks in such a manner that when any disk passes from the 9 to the 0 state, a motion is imparted to the disk in the next more significant position such that it passes from state i to i+1.

As a rule, mechanical and electromechanical computing aids used for normal computational work employ the decimal system. This is because it is a relatively simple matter to define and maintain ten distinct positions of a rotary element. In electronic computing aids, where a number is represented by such things as the amount of charge on a dielectric material, the state of magnetization of a magnetic element, or the voltage at some point in an electronic circuit, the use of the decimal system produces difficulties. These can all be attributed to the fact that it is difficult to control the placement of an electrical element precisely into one of ten stable states, and equally difficult to read the states of circuits to such precision. Because of such practical difficulties, all electronic digital computers are formed from binary elements, i.e., switching and storage devices which need assume only two distinguishable stable states. Hence, use of the binary rather than the decimal system is dictated. This is because two (or some power of two) is the most economical radix to use with binary elements simply because all possible configurations of a group of binary elements can then be utilized. The use of the binary system presents no great difficulty, and there is no intrinsic reason why one must use the decimal number system. One may choose any radix for the base of a number system. The Babylonians used the sexagesimal system (i.e., the base was 60, as opposed to 10 for the decimal), the Mayans used the duodecimal system. Outside of psychological reasons, stemming from its common use in all phases of human commerce, the decimal system is not the best to use for computing.

Even though numbers are represented within a machine in the binary number system, conversion between the two types of number systems can take place at the inputs and outputs of a machine so that, as far as the user is concerned, the machine operates in the decimal system. To facilitate this conversion, the binary-coded decimal system (see Chapter 6) may be used in the internal storage elements of a computer as well as in its input and output equipment.

#### 1.5. Quantization

Media used for the recording of information are usually capable of responding to a continuous range of input signal intensity, from the so-called threshold level to the saturation level. For example, information can be represented on magnetic tape by the intensity of magnetization of specified areas on the tape, and this intensity is determined, over the threshold to saturation range, by the magnitude of current applied to a recording head. A measure of the amount of information stored in any one area is given by the total number of levels of magnetization that can be recorded and sensed. Ideally, it would be desirable to store a large amount of data with a minimum amount of storage media. However, in practice a compromise must be made in order to reduce the probable error in interpreting the recorded information when sensed at some later time. Use of quantization in the recording and sensing processes allows one to trade efficiency of storage for a greater probability of correct interpretation of the data.

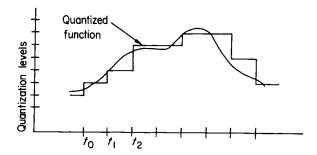

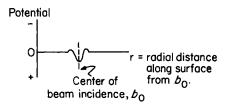

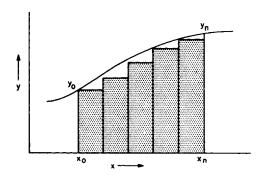

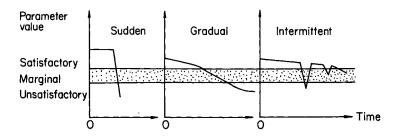

Fig. 1.1. Quantization of a function

The nature of the quantizing process is shown in Fig. 1.1. Note, first of all, that the range of values of the function is divided, on some basis, into a number of smaller subranges. The values selected to define the subranges are called levels of quantization. One way of quantizing a function is to replace its value by the value of the nearest level of quantization whenever it passes the halfway point between two levels, the value of the quantized function remaining constant between such occurrences. However, in practice, and as shown in Fig. 1.1, the quantization process is usually associated with a fixed period sampling process wherein the original function is inspected at times  $t_0, t_1, t_2 \ldots$  and its value replaced by that of the closest level of quantization at these times. In a synchronous digital computer, the instants of time,  $t_i$ , would be specified by a timing

source referred to as a clock (see Chapter 3). Often one uses a quantizing process without realizing it as, for example, when reading a dial, gauge, or scale to the nearest unit.

The way in which quantization can be employed to reduce the probability of misinterpreting stored data will now be described. For the purpose of illustration, consider again a magnetic storage medium. For each state of magnetization of the medium, there is a finite probability that an accidental event will cause a transition to some other state of magnetization. Of course, the greater the separation between two states the less the probability that an accident will occur to cause the transition from one state to the other. Accordingly, the difference between levels of quantization can be defined in such a way that the probability of a signal on one level being mistaken for that on an adjacent level is less than a specified amount. An ideal, absolutely stable state of a storage medium exists only if a perfect switching action is involved, i.e., if an impulse of energy is required for a transition between two states, and only in this case could the probability of misinterpreting stored data be reduced to an absolute minimum. In practice this situation is adequately approximated by choosing levels sufficiently far apart that a large amplitude signal is required to switch the storage element from one level to the other. The passive storage elements used in all contemporary electronic digital computers are referred to as binary elements because of this type of arrangement. Bounds are specified about each level within which the sensing device reports the same value. This is done so that variations from the specified levels, due either to small irregularities in the medium or small transitions that may have occurred, are not sensed. Two advantages of the binary quantizing process are apparent. It allows for exactness and for reproducibility of results. Binary quantization reduces the problems associated with measuring physical parameters to a simple determination of the presence of signals near the threshold and saturation levels. Thus, the uncertainties entering into measurement are replaced by the relative certainty of detection of a large amplitude signal. Binary quantized data can be processed with relative immunity to the compounding of small errors that occurs in a nonquantized data system. In a binary system the end result of a series of operations will always be the same no matter how many times it is repeated. This is an especially important factor in the processing of commercial data where money and other items must be accounted for, not to within some tolerance of error, but to a precise figure.

Of course, for an increased efficiency of storage multilevel storage devices could be used if the additional levels could be recorded and

sensed without an objectionable increase in the probability of error of interpretation.

#### 1.6. The Evolution of Computing Aids

It is only natural to expect that means for representing and processing information would be influenced by the technological level of each age. We have already observed that man first counted by means of his fingers, and later used line segments to represent elements in a collection. In early forms of the abacus, developed over 5000 years ago, a number was represented by the pattern in which a set of pebbles was arranged. Later the abacus evolved to its present form which differs principally in that beads are threaded on wires or thin rods that define the columns and the whole is enclosed in a frame. There were no significant new developments in computing aids until the seventeenth century. Then in 1642, the first desk calculator was invented by Blaise Pascal. It could perform addition and subtraction, and its operation was based on the use of toothed wheels. Leibnitz designed the so-called stepped wheel, and improved upon Pascal's machine by devising a means of multiplication by repeated addition. A machine with this feature was completed in 1694, but suffered from mechanical imperfections. Further improvement on Pascal's machine was made by Thomas de Colmar who, in 1820, produced the first successful machine for multiplication. In 1878, the Swedish engineer Odhner, invented the pin-wheel method of adding numbers from one to nine. His patents were subsequently incorporated in the Brunswiga hand calculating machines. The first successful key driven adding machine, the Comptometer, was developed in 1887 by D. E. Felt. After this time, a number of significant improvements were added by new designs as well as additions to old ones. Single operation multiplication was introduced by Leon Bollée in 1888. In 1889, a printing feature was added to the Comptometer. After 1910, electric drive motors were added to mechanical calculators. This allowed more complex circuits to be used, since keys or light parts of the machine's internal mechanism could be used to actuate control switches.

In the era of the Industrial Revolution, the idea of mechanical automata achieved a marked popularity, and many ingenious mechanical devices were developed which, upon being actuated would follow a prescribed set of motions. Two relatively important devices were developed at this time to control the motions of two quite different mechanisms. From them have evolved two input—output media widely used with present electronic digital computers, and which in their present form are basically

similar. One of these devices was a metallic disk or cylinder upon which bumps were placed at designated points to control the times at which different notes were struck in a music box. From it were developed player piano rolls and various types of punched paper tape, most notably those used to control teletype equipment. The other was the Jacquard card, used to control the weaving of patterns into cloth. It served as a model for the development of the Hollerith punched card. The holes in these cards are sensed by electric circuits connected to metal brushes that make contact through the holes. The punched card, on which a number is represented by a pattern of punched holes, was not conceptually an advance over the abacus. However, it afforded the first significant practical means of semiautomatic data processing. Its importance was derived from the many special types of electromechanical units that could be, and were devised for the rapid sorting, interpretation, and manipulation of data on cards. By 1945, punched card machines were in widespread use throughout the world for the tabulating, sorting, and analysis of data for accounting and statistical purposes.

Another important contribution, current with the development of punched card machines, was the development of relays for controlling complex telephone switching networks. These switching systems showed that it was possible to perform complicated logical operations with relays, and to obtain reliable operation by self-checking techniques. In 1938, Stibitz developed, at the Bell Telephone Laboratories, a relay computer capable of addition, subtraction, multiplication, or division of complex numbers and which could be remotely controlled. In subsequent relay computers a self-checking code was introduced to detect a malfunction in the transmission of numbers. Subsequently, other relay computers were developed at the Bell Telephone Laboratories. These machines and the Harvard Mark I Calculator, developed jointly by IBM and Harvard University, were the pioneer efforts in relay computers. The latter machine was the first large scale general purpose digital computer to be completed (1944). Punched cards were used as the input and main storage medium, and relays were used for the arithmetic unit. About the same time, the first electronic digital computer was built. This machine, termed the ENIAC (Electronic Numerical Integrator And Calculator), was developed by the Moore School of Engineering at the University of Pennsylvania. It contained about 18,000 vacuum tubes. The last decade has seen the rapid development of the stored program electronic digital computer. This type of machine has wide application because it can perform many types of information processing operations at high speed and without human intervention, once a suitable program of instructions has been entered into it.

Although the state of development of commercially available digital computers was quite limited up to the time of World War II, the concept of a stored program automatic digital computer had been worked out by Charles Babbage in about 1833 in his design for an "Analytical Engine." The plan of this machine called for 50 digit numbers and a storage capacity of 1000 numbers, and it was intended that Jacquard cards be used in two ways. So-called "operation cards" were to be used to convey instructions to the arithmetic unit, and "variable cards" to specify the locations in storage from which two operands were to be taken and the result of a computation stored. The plans called for punching the output data on cards, for the purpose of having them available for future computation. Also, there was to be a device for printing results directly and a means for producing stereotype molds to be used for printing additional copies. Babbage's writings show that he was aware that the same language could be used for numbers and instructions, and that the machine could be made to modify its own program in accordance with the results of computations.

# 1.7. The Representation of Numbers in an Electronic Digital Computer

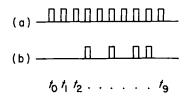

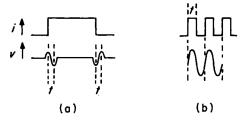

We have seen that in a mechanical digital computer, a number is represented by discrete positions of a shaft and numerical information is transmitted between these elements by the coupling of discrete rotary motion. In an electronic digital computer, a number is commonly represented in binary form by the current state of a set of storage elements each of which is capable of, and restricted to, assuming two stable output voltage levels. Information is transmitted between these elements either serially in the form of voltage pulse trains on a single information channel, or in parallel by the signals currently present on each of a set of information channels. Each of the pulses in a train may represent a single increment (corresponding to counting), or a set of pulses beginning and ending at defined positions in time may represent a number in some binary coded form (corresponding to a positional notation). The former representation may be termed a unitary weighted pulse train, and the latter a binary coded pulse train. Both types of serial representation are shown in Fig. 1.2. In the binary coded pulse train, the first bit of the train to appear represents the least significant bit of the number. This is for reasons associated with the computation processes. Since the electrical waveform convention is that time flows from left to right, the order of digits in a number so

represented will be reversed from the order of digits in the conventional written notation.\*

Fig. 1.2. Serial representation of a number by a pulse train

- (a) Unitary weighted pulse train: the ten pulses represent ten unit increments

- (b) Binary coded pulse train: The presence of a pulse at time t<sub>i</sub> represents an increment of 2<sup>t</sup>. The number shown is 2<sup>3</sup> + 2<sup>5</sup> + 2<sup>7</sup> + 2<sup>8</sup> = 424

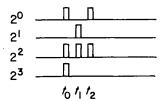

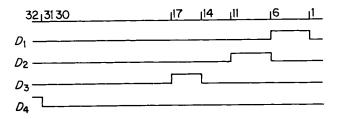

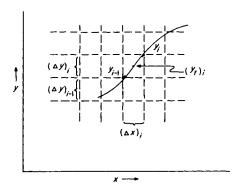

The parallel representation of a number within a computer is always in a binary coded form where different weights are assigned to the different channels in a group. Figure 1.3 illustrates how a four bit number would appear in a parallel representation. At each time,  $t_i$ , there may or may not

Fig. 1.3. Parallel representation of a number  $N = b_0 2^0 + b_1 2^1 + b_2 2^2 + b_3 2^3$  where  $b_i = 1$  or 0 At  $t_0$ , N = 13;  $t_1$ , N = 6;  $t_2$ , N = 5

be a pulse on each of the lines. Each line has an assigned weight as shown, and the value of the number, N, appearing at any time is the weighted sum of the pulses on all the lines. An important distinction between serial and parallel weighted numerical representation is that in the

<sup>\*</sup>Our numerical symbols were introduced from India by the Arabs who read from right to left. When introduced into English, the matter of reversing the order of a group of numerals to conform to our reading convention was overlooked. However, in reading it is not inconvenient to read the higher orders of a number first, for it is the complete configuration that conveys the value.

former case different weights are assigned to different time positions, i.e., the weight of a pulse is determined by the relative time of its appearance at a given point, while in the latter case different weights are assigned to different physical locations.

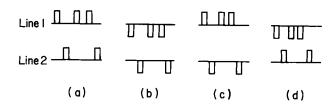

Since there may be either positive or negative pulses on a line, a choice may be made as to how to represent 0's and 1's. For example, a positive pulse may be chosen to represent 1, and a negative pulse to represent 0, or vice versa. When it is desirable to use pulses of only one polarity, the presence of a pulse may be used to represent 1 and the absence of a pulse 0, or vice versa. If a unitary weighted pulse train represents information that has been generated asynchronously, then a single line may be used for transmitting either positive or negative increments, but not both. To provide for both, two lines must be used, the presence of pulses on one line representing positive increments and the presence of pulses on the other representing negative increments. Either positive or negative pulses may be used to represent increments on either line, as shown in Fig. 1.4. The choice will depend on the characteristics of circuit elements. Schemes (a) and (b) are most commonly used.

Fig. 1.4. Asynchronous unitary weighted pulse trains

The use of a numerical biasing technique permits the use of a single line to transmit unitary weighted information of both positive and negative sign if the information appears synchronously. Using this technique, the presence of a pulse on the line at any time defined by the timing source indicates a positive increment while the absence of a pulse indicates a negative increment. This technique depends on generating a train of alternate 1's and 0's in a system in the absence of positive or negative increments. This type of information transmission is sometimes referred to as binary information transfer, while the method described in the preceding paragraph is termed ternary transfer.

In a binary coded pulse train, a single line is always sufficient for the representation of positive or negative numbers. The sign of the number is indicated by the presence or absence of a pulse in a position reserved

for sign identification. The number may be represented either as an absolute value plus sign, or a complementary system may be used to represent negative numbers. (See Chapter 6.)

#### 1.8. Arithmetic Processes in Digital Computers

A considerable amount of space in the text is devoted to a description of different ways of performing the commonly encountered operations of counting, addition, subtraction, multiplication, and division in a digital computer. Since these operations are apparently so simple when performed in our heads or with pencil and paper, some words of explanation may be in order. First of all, the characteristics of different physical elements used to perform these operations must be considered. A procedure suitable when using one type of element may not be suitable when using another. Also, certain logical formulations of these processes may be more economical equipment-wise than others. Finally, a vast number of different types of serial, parallel, and serial-parallel, i.e., semiparallel, operation is possible, some more suitable with particular physical elements than others. The average person, in performing computations, functions in a serial manner, i.e., he performs one operation at a time as, for example, in adding where he adds one column and produces one digit of the sum at a time. Since he can only write one digit at a time his serial arithmetic operations are adequate. However, within a digital computer, it is possible to incorporate control circuits that cause all digits of the addend and augend to be sensed simultaneously. The sum can then be recorded in far less time than required by serial arithmetic operation. The purpose of all parallel arithmetic operation is to decrease the time required for computation. This is paid for by an increased amount and complexity of equipment. When serial operation is not fast enough, and parallel operation is too expensive, a compromise may be made with serial-parallel procedures.

#### 1.9. Redundancy

Let us return again to the subject of numerical representation used by the Romans. Not only were different symbols used for different orders, e.g., X for 10, C for 100, etc., but these symbols were written by convention in an ordered relation. For example, 2153 was written as MMCLIII, not as, say CLMMIII, LCIIIMM, etc. However, if one were to come upon one of the latter representations, he could still interpret it correctly. The Romans, though fond of order, did not appreciate the fact that placing symbols, by convention, in an ordered relation makes it unnecessary to have different symbols for different orders. Consequently,

the Roman notation had a redundancy which is not present in modern positional notation. As a rule, redundancy is a measure of how efficiently a particular set of symbols or type of notation conveys information. (In Chapter 9 the subject of redundancy is considered in relation to error detection and correction). The use of a positional notation allows a small set of symbols to be adequate for representing any magnitude, and a proper choice of radix (the number of different symbols) allows large magnitudes to be represented by a reasonable number of symbols.

It is not unusual for primitive notations to exhibit redundancies. The same can be said for initial designs of new equipment. In an "idealized" type of world where no unintentional disturbances, i.e., accidents, were possible, and everything always functioned as designed, redundancy would serve no purpose. However, in reality it often proves useful as a means of reducing or eliminating the detrimental effect of an accident. How this can be done will be discussed, for certain types of failures, in Chapter 9. Here we only wish to point out that once the logical requirements of a piece of equipment such as a digital computer are better understood, redundancy may be minimized for the sake of economy. However, even then one may find it desirable to incorporate certain intentional redundancies for the sake of improving the reliability of performance of a system composed of nonideal physical elements.

#### 1.10. Computer Applications

Human progress is dependent on efficient means for the processing of information, as an aid to the creative processes of thought. Simply for the purpose of drawing an analogy, we will consider first certain functional similarities between information processing by humans and machines.

When an individual is confronted with a problem, he may call upon intuition, learning, and experience to solve that problem. All of these terms refer to the fact that he has available inherited and acquired information pertinent to the solution of specific problems. This information is stored (in ways as yet undetermined) in his memory. This memory is of sufficient capacity to store vast amounts of information pertinent to the solution of specific problems, and there are mechanisms for integrating various sections of this stored data in a manner appropriate to the solution of new and more complex problems. It will be shown in Chapter 2 that before a digital computer can produce the solution to a specific problem, it, too, must be furnished with information—in the form of a program which describes a specific sequence of operations to be performed. If a computer is to be able to solve different problems, it must be furnished with appropriate programs. These are stored in its memory.

referred to as the store, to which access may be gained by means of a control unit.

Though a stored program digital computer is conceptually a simple device, its high rate of operation and facility for arithmetic and logical operations, coupled with the ingenuity of its users, make it of great utility. Outside of their importance to many specific areas (delineated below) such machines are contributing materially to the acquisition of knowledge by processing vast amounts of data and performing computations to check new theories. An important indirect benefit they provide is the introduction of improved procedures and terminology to areas previously limited in their use of systematic mathematical and logical formulations.

Application of digital computer technology to more fields of human endeavor is increasing rapidly. In the business world, digital computers facilitate and accelerate the extensive routine data processing vital to daily commerce, e.g., processing of credit transaction data, customer billing, inventory control and various accounting operations. Information processors are essential to the military in many areas, e.g., in military intelligence data processing, early warning systems, command and control systems; for automatic navigation of ships, aircraft and space vehicles, automatic control of weapons systems, automatic checkout of complex electronic systems prior to use. Computers can be used in industrial automation for data refinement and assimilation, scanning of instrumentation for detection of alarm conditions, automatic data logging, evaluation of plant performance and control of machines, plants and processes. Computers can be used in factories to improve record keeping and scheduling of production. They can be applied to the regulation of traffic, e.g., 1) aircraft, train, steamship and freeway traffic, 2) messages to be routed through complex communications networks (such as satellite relay systems), 3) commodities like natural gas and oil, whose flow through hundreds of miles of pipeline distribution systems must be economically controlled. Application to management problems, whether in industrial, governmental or military areas, will be extensive because the amount of data upon which decisions must be based is increasing while the time available for decision making is decreasing. Some interesting applications on the horizon are: 1) teaching machines for efficient, automatic factual instruction, 2) machines to aid medical diagnosis, 3) large scale information storage and retrieval systems.

One of the most intriguing areas of investigation is the application of artificial intelligence systems\* to problems which, though well defined, are too difficult for complete analysis. Obtaining a solution to some of these

<sup>\*</sup>For a lucid survey of this subject see M. Minsky [1961] Steps toward artificial intelligence, *Proc. IRE*, 49, 8-30.

problems by an exhaustive search and test of all possibilities would require an unattainable amount of time even with the fastest machines. Therefore, various techniques are being investigated to produce computer programs that limit the search to manageable proportions. For example, there are:

1) pattern recognition programs which, by extracting significant features from a totality containing much that is irrelevant, classify problems into categories for which specific problem solving procedures may be prescribed,

2) learning programs which generalize on accumulated experience, 3) planning and administrative procedures for attacking the over-all problem and its interrelated parts, 4) inductive methods which, given a model of a universe, can generate useful predictions for it. All of these higher level information processors are based on externally observable features of schemes by which men attack new problems.

A mental process important to creativity is that by which relations between events are recognized, stored and new information being associated and integrated to form new ideas. This is usually on a gross level at first, but with continued refinement can lead to a useful model or set of laws which state these relationships in a quantitative manner. No one has yet brought forth a means by which a computer could create a useful new concept. Even if a machine could generate new theories, say by some statistical process of connecting various facts and testing them for consistency, it would still lack criteria for selecting meaningful ones unless well defined abstract and/or physical goals were implanted by a program (realization of a physical goal requiring interconnection between the computer and appropriate actuators).

Application of digital computers to higher level types of information processing has brought renewed speculation on whether machines can be made to think (reminiscent of earlier descriptions of digital computers as electronic brains). This speculation is meaningless since "thought" has never been adequately defined and serves merely as a label for a complex of mental processes whose mechanisms are not understood. The term "artificial intelligence" simply refers to higher level information processing performed by machines which have been furnished with heuristic and/or algorithmic devices for solving problems. This extension of man's intellect does not degrade his dignity, as some suggest, but is a further expression of his mental powers.

In case you are chagrined by the suggestion of being only an intelligent machine we submit an observation from Karl Jasper's *The Future of Mankind* (translated by E.B. Ashton, University of Chicago Press, 1961): "Intelligence alone loses sight of final ends, of life itself, of the totality of conditions of life in the pursuit of particular realizable goals. Something more must control as well as animate mere intelligence."

# 2. The Nature of Automatic Computation

# 2.1. Elements of Information Processing Systems and Types of Digital Computers

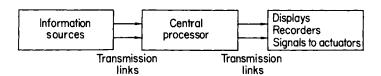

Before discussing the structure and techniques for utilization of digital computers, a few words may be in order concerning information processing systems in general. The term, information processing system, is used here to include all systems containing the following elements. (1) Sources of information from which data is obtained. (2) Transmission links which convey the source data to a central processor and from there to locations of end use. (3) The central processor which applies elementary and/or complex transformations to the original data to obtain a final set of data in a desired form. (4) Output terminals for the processed data, including cathode ray tubes or other visual displays, printers, recorders, and input signals to actuators in control systems.

Fig. 2.1. Elements of an information processing system

The elements of an information processing system are shown in Fig. 2.1. Many devices and methods have been developed for the purpose of accomplishing each of the specialized functions:

- (1) Information collecting devices: instruments for sensing pressure, temperature, electromagnetic radiation, fluid flow; composition analyzers; radars; human beings; etc.

- (2) Transmission links: phone, teletype, coaxial lines, radio, vehicular transportation, human beings, etc.

- (3) Central processors: desk calculators, sequencing devices (or programmers), coding devices, electronic digital computers, regulators, analog computers, human beings, etc. A central processor may perform one or more of the following types of operations on input data: arithmetic,

logical transformations, sorting and classification, conversion from one type of code or numerical representation to another, storing, sequencing.

(4) Output terminals: For scientific, engineering, or business studies, the outputs of a digital computer are usually graphs or printed data. For commercial applications such as billing of notices to customers, or payroll computations, the output is in printed form. In control applications, e.g., in industrial process control systems, or airborne navigation, flight management, and weapons control systems, a number of simple monitoring displays are provided in addition to the electrical signals generated for controlling the operation of various actuators within a regulator or servo system. In other control applications, e.g., tactical data systems for processing radar, logistics, and intelligence information, or air traffic control systems, input signals to various actuators must also be provided, but the major emphasis is on a large number of displays, including cathode ray tubes, display counters, and yes—no indicators, to inform responsible personnel of the various aspects of a situation as it develops.

When a "general purpose" digital computer, or GP machine, is referred to, a central processor is implied that is capable of any of the operations listed under item (3). A few words are in order concerning the term "general purpose" computer. Unfortunately, it often leads to confusion or awkward types of descriptions. This tag became affixed to the first large electronic digital computers. It arose because of the flexibility of these computers in solving many different types of problems. This flexibility derives from two principal sources. First, these machines are capable of executing a large number of different elementary operations, from which more complex operations can be obtained by combining the elementary ones. Second, the manner in which elementary operations are to be combined for the solution of a specific problem is specified by a sequence of coded instructions, termed a program, which is inserted in the computer's central memory known, too, as the main or central store, and which controls the execution of a problem. Different programs are inserted for the solution of different problems.

At a later date, similar computers were designed for specific applications. This allowed simplifications to be made, since only a single fixed program had to be provided for. However, the tag "general purpose" had already been assigned to this class of equipment, and therefore machines designed for a special function were termed fixed program GP machines.

Another class of machines was devised primarily for the purpose of solving differential equations. Its chief difference from the GP is that only single bits, i.e., increments of information rather than whole numbers, are transferred on its internal communication lines. This type of machine

is referred to as a digital differential analyzer, or DDA. It can be used to solve any of a number of different types of algebraic as well as differential equations, and, in this sense, is a general purpose computer. Most DDA's in use are of the fixed program type, designed for incorporation, separately or in conjunction with a GP machine (the two usually sharing a large capacity memory), into a control system. In this case, only a particular set of equations has to be solved, subject to different initial conditions and forcing functions.

To conclude, if a particular machine is designated as a special purpose or general purpose type, it is not always clear whether reference is being made to a GP machine or a DDA. One way out of this confusion is to refer to one type of machine as an absolute, arithmetic, or integral transfer computer and the other as an incremental or incremental analyzer, or incremental transfer type of computer. The additional classification of "general" or "special" purpose is made according to whether the machine has a variable or fixed program.

#### 2.2. The Nature of Automatic Computation

Our purpose here is to demonstrate the simplicity of the concepts involved in the design of a general purpose arithmetic digital computer. First of all, it must be emphasized that a computer cannot perform any mathematical or logical operation beyond the capability of a suitably trained human being. Its great utility is derived from the high speed capability of the electronic circuits used to perform arithmetic and logical operations and other functions. There are descriptions of such circuits in Chapters 4, and 5. At this point, we will consider the fundamental nature of computational processes\* performed by human beings, and how these processes may be simulated by an automatic computer.

Consider first how a human being with only pencil and paper performs a computation. Suppose, for example, that he wishes to determine how much money he has spent during the previous weeks. He has several bills, each of which has some amount of money specified on it. These bills can be considered as storage devices because they retain information, making it available when needed. To produce the sum total, he would most likely list the amounts of the individual bills on a piece of paper, and then proceed to find the sum. The following different types of elements entered into the operations described:

<sup>\*</sup>Since these processes were evolved to facilitate computation by human beings, they may not necessarily be the best methods for computers. It may develop that specialized methods of computation will evolve, and eventually change our present day techniques of mathematical education.

- (1) An input element: The pencil, controlled by the human being, which effected the transfer of the individual pieces of information from several places (the individual bills) to a single place (the tally sheet) where the required summation could be performed.

- (2) Storage elements. Permanent: The bills which retain information and make it available when needed. Temporary: The tally sheet. After the sum is obtained the information on this sheet of paper may be erased, if required for no additional purpose.

- (3) Arithmetic element: Certain parts of the brain which are capable of performing the operation of addition. The inputs to the brain's arithmetic section are derived via visual signals received from the pencil marks on the paper.

- (4) Output element: The pencil, by means of which the human being records the answer on the sheet of paper.

- (5) Control element: The control element controls the flow of information between the other elements. In this case it is the human being who determines from where information is to be accepted, what types of operation to perform, and where processed information (the answer) is to be stored.

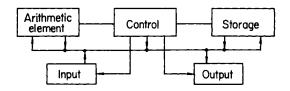

Fig. 2.2. Interrelation of elements in a digital computing system

The interrelation of the various elements is shown in Fig. 2.2. In our example, the data transmission lines shown in Fig. 2.2 are of two types. Information is transmitted from the paper to the eye via light rays, and from the eye to the brain via electrical signals propagated along a nerve bundle. It is transmitted from the brain to the paper via electrical signals which cause the fingers of the hand to move a writing instrument so that it forms the desired characters.

Certain variants of the operations described are possible. For example, the use of pencil and paper as input—output and temporary storage elements may be eliminated. Information from the bills may be sent to temporary storage positions in the brain, the computation performed in the brain's arithmetic elements, and the final answer stored in other storage elements of the brain. However, not many people have developed the

facility of performing a long sequence of arithmetic operations "in their head" and therefore mechanical aids are utilized. An important aid is the electromechanical desk calculator which permits long sequences of arithmetic operations to be carried out in less time and with less fatigue for the operator (consequently with less chance for error) than computation with only pencil and paper.

The types of operational capabilities required of a general purpose electronic digital computer will now be considered. An important point to remember is that the function of performing arithmetic and logical operations comprises only part of a computing system. Another important function is the transfer of information from one locality to another. In an average computation using a desk calculator an appreciable percentage of time is spent in information transfer operations, e.g., transferring information from original sources to data sheets, copying information from data sheets into the calculator, copying intermediate results from the calculator onto sheets of paper, preparing sheets of paper with the final tabulated answers.

It becomes apparent that in order to increase the speed of a complete computational process, it is necessary to increase the speed of the transfer operations as well as that of the arithmetic operations. This implies the elimination of the human operator once the computation is begun, for he is the bottleneck. Clearly one gains very little by decreasing the time required to perform an arithmetic operation from say, 1 sec to 1/100 sec, if at the end of each operation a human operator has to spend several seconds copying information out of and inserting new information into an arithmetic unit.

The utility of present electronic digital computers results not only from their basic high speed of operation, but also from the fact that they can perform without human intervention all the steps required in a computation involving thousands of operations. This is possible because of three distinct reasons. First of all, a method for solution of a given problem can be stated in terms of a relatively short program which lists all the elemental arithmetic, logical, and transfer operations that are to be performed in the course of solving a problem. This program is prevented from becoming too long by the use of iterative problem-solving techniques in which a sequence of operations is repeated until a desired result is obtained. This makes it unnecessary to write new steps for each repetition of the sequence. Instead, one merely writes the sequence and specifies that it be repeated, with new initial conditions each time, until a desired result is obtained, at which time an indication is provided by the machine. Second, the control unit of the computer causes the individual steps of a computation to be carried out as directed in the program. Third, the computer can execute conditional transfer instructions. This permits the operations in a subsequent iterative section of a program to be initiated without human intervention upon the successful completion of a preceding iterative section of a program.

The general types of instructions that a computer should be capable of executing are:

- (1) Combination transfer and arithmetic or logical instructions. These instructions cause information from specified memory locations to be brought to the arithmetic unit where operations such as the multiplication, division, addition, subtraction, and comparison of two numbers are performed. The result is left in the arithmetic unit at the end of an operation.

- (2) Operations involving the arithmetic unit only with no reference to the memory; e.g., shift instructions.

- (3) Transfer instructions which cause a transfer of information from one part of the computer, e.g., the memory or arithmetic unit, to one or more other parts of the computer.

- (4) Control transfer instructions. There are two major types of control transfer instructions. The unconditional transfer instruction transfers control to an instruction out of sequence. The transfer may be to auxiliary programs outside the main program or may serve to skip instructions in a given sequence. This type of transfer does not involve the use of any data not contained in the instruction itself. One conditional transfer or test instruction operates as follows: If the number in the arithmetic unit (the accumulator) is  $\geq 0$ , control will proceed to the next instruction in sequence, but if the number is < 0, control will be shifted to the instruction located in the memory position specified by the conditional transfer instructions (for some variants see Section 7.2).

- (5) Instructions involving the transmission of information from the input units and to the output units.

## 2.3. Computation by a Stored Program Digital Computer

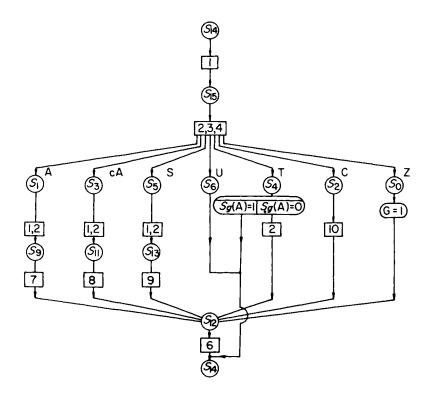

The following discussion will show how automatic computation can be achieved even by a computer capable of executing only a very few simple instructions. Assume that the computer contains the following elements (shown schematically in Fig. 2.3):

Fig. 2.3. Principal storage units in a digital computer

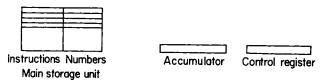

- (1) A main storage unit which has adequate capacity to hold the coded representations of the instructions in a program, as well as numbers that must be stored, e.g., constants, initial values of problem parameters, and numbers generated during the computation which must be stored temporarily.

- (2) An accumulator, which is a special storage register associated with the arithmetic unit. It holds an operand in a form accessible to the arithmetic unit, allowing certain operations to be performed on it. In operations involving two operands, it holds one while the second is located in the store and transmitted to the arithmetic unit. Also, it serves to store a result until it can be transmitted elsewhere.

- (3) A register called the control register whose contents indicate from which location in the main storage to obtain the instruction to be executed next.

Assume also that the computer can execute only seven different instructions. The nature of these instructions as well as mnemonic codes for them are shown in Table 2.1.

TABLE 2.1. Instruction repertory of a simple, hypothetical computer

| Code | Instruction                                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cA m | Add the contents of storage location m to the cleared accumulator.                                                                                                                      |

| A m  | Add the contents of storage location m to the contents of the accumulator, leaving the sum in the accumulator.                                                                          |

| Sm   | Subtract the contents of storage location m from the contents of the accumulator, leaving the difference in the accumulator.                                                            |

| Сm   | Copy the contents of the accumulator into storage location m.                                                                                                                           |

| Um   | Transfer the address m to the control register.                                                                                                                                         |

| Tm   | Test (i.e., inspect) the sign of the number in the accumulator. If the number is negative transfer the address m to the control register. If the number is zero or positive do nothing. |

| STOP | Go into an idle state.                                                                                                                                                                  |

The code used to represent an instruction consists basically of two parts: 1) an operation field in which is placed a code symbol for a specified operation, 2) an address field in which appears a number whose meaning depends on the operation. In the one-address type of machine described here (see Section 7.5.4 for a description of multi-address instructions) the number in the address field of certain instructions (for example, cA m, A m, S m and C m) indicates a storage location whose contents are to be transmitted elsewhere or altered; in transfer of control instructions (for example, U m, T m) the number in the address field indicates an address to which control will or may be transferred; in a binary

shift instruction it indicates the number of binary places to be shifted. The list of instructions in Section 7.2 indicates other uses to which the address field may be applied. Because failure to distinguish between an address and data stored at that address can be a major source of difficulty in writing and understanding programs, sometimes parentheses are placed about the number in the address field to emphasize that the contents of the designated location are being referred to. However, in this text parentheses will not be used in the instruction codes.

The STOP instruction defined in Table 2.1 implies that the computer is capable of being in either an active or idle state, and that external means are provided for placing the computer in one or the other state. This is the case and the actions of the computer in these states is outlined below.

| State   | Operations Performed                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------|

| Idle:   | Do nothing                                                                                            |

| Active: | When not otherwise occupied:  (1) Add 1 to the number in the control register, leaving the sum there. |

(2) Read and execute the instruction in the storage location designated by the new number in the control register.

We will specify that when the computer is first set to an active state, the contents of the control register are set to zero. As a result of operation (1) in the active state, the number in the control register is changed to 1 and the instruction stored in the storage location designated by 1 is executed. After the execution of each instruction, the instruction in the next consecutively numbered storage location will be executed. Instructions U m and T m can cause an exception to this normal sequence of operations. If the instruction U m appears in storage location i, the next instruction executed after it will not be that in storage location i + 1, but rather that in storage location m. If the instruction T m appears in storage location j, the next instruction executed after it will be that in location j + 1 if the number currently in the accumulator is positive or zero; otherwise, it will be the instruction in location m. U m and T m are referred to as unconditional transfer and conditional transfer (or test) instructions, respectively.

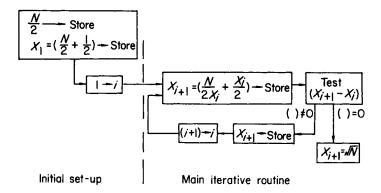

The way has now been prepared to show how a large number of arithmetic and logical operations that may be required in the solution of a problem can be performed without the aid of outside intervention, provided the computer has certain elements and capabilities which have been described. As an example of automatic computation consider the program shown in Table 2.2. It is designed to find the highest factor of an integer, x. Each instruction is executed after its address, shown in column one, appears in the control register. The third column shows the contents of the accumulator after the execution of each instruction.

| Address | Instruction        | Contents of Accumulator    |  |  |  |  |

|---------|--------------------|----------------------------|--|--|--|--|

| 001     | cA 104             | 0                          |  |  |  |  |

| 002     | S 101              | - x                        |  |  |  |  |

| 003     | A 102              | $-x+jy_{\epsilon}$         |  |  |  |  |

| 004     | T 003              | $-x+iy_{\epsilon}$         |  |  |  |  |

| 005     | C 103              | $-x+iy_{4}$                |  |  |  |  |

| 006     | cA 104             | 0                          |  |  |  |  |

| 007     | S 103              | $x-jy_{\epsilon}$          |  |  |  |  |

| 008     | T 010              | $x-iy_i$                   |  |  |  |  |

| 009     | STOP               | 0                          |  |  |  |  |

| 010     | cA 102             | y <sub>4</sub>             |  |  |  |  |

| 011     | S 105              | $y_4 - 1$                  |  |  |  |  |

| 012     | C 102              | $y_{i} - 1$                |  |  |  |  |

| 013     | U 001              | $y_4 - 1$                  |  |  |  |  |

|         | Numbers \          |                            |  |  |  |  |

| 101     | <u> </u>           |                            |  |  |  |  |

| 102     | y <sub>i</sub> * \ | Constants and intermediate |  |  |  |  |

| 103     | <del>-</del> (     | results are stored here.   |  |  |  |  |

| 104     | 000                |                            |  |  |  |  |

| 105     | 001                |                            |  |  |  |  |

TABLE 2.2. Program for determining the highest factor of an integer, x.

An explanation of the program itself follows: The instructions of the program are placed in correct sequence in locations 001 through 013; 101 through 105 are reserved for storage of numbers. Location 101 holds the integer, x; 102 and 103 serve as temporary or working storage for numbers generated in the course of the program; 104 and 105 store the constants required by the program.

The instructions in locations 001 and 002 clear the accumulator and enter -x into it. The instruction in location 003 produces  $-x + y_i$ . Each time instruction T 003 is obeyed, control is returned to location 003 until, after j cycles, the sign digit of the accumulator indicates that  $-x + jy_i$  is either a positive number or zero.† When this occurs, the instruction T 003 advances control to location 005.

<sup>\*</sup>The number stored here before the start of the program is the initial trial factor  $y_0 = x - 1$ .

<sup>†</sup>In a system of numerical representation (see Section 6.1.4) in which the sign digit of zero is the same as that of a positive number, testing of the sign digit (which is the operation performed in a U m or T m instruction) will not distinguish between the two cases.

In order to detect whether  $-x + jy_i$  is a positive number or zero, the quantity  $-x + jy_i$  is converted by means of the instructions in locations 005, 006 and 007 into the quantity  $x - jy_i$  (by storing  $-x + jy_i$  in location 103 and then subtracting it from the cleared accumulator). If  $-x + jy_i$  is a positive number the conversion results in a negative number, if it is zero the conversion has no effect. If  $y_i$  is a factor of x,  $x - jy_i$  is zero. In this case, the instruction T 010 advances control to location 009 and completion of the program. If  $y_i$  is not a factor, the converted quantity  $x - jy_i$  is not zero and T 010 advances control to location 010. The instructions in locations 010 through 012 produce a new trial factor  $y_i - 1$  and store it in location 102. Instruction U 001 permits the whole sequence of instructions to be reiterated with  $y_i - 1$  as the new trial factor.

All the integers from  $y_0$  downwards will be tested until finally one is found that is a factor. When this occurs, the number in the accumulator will be zero when the test instruction T 010 is executed, so control will be advanced to the instruction in location 009. The stop instruction puts the machine into an idle state, and the highest factor of x will be found in location 102.

The preceding example has shown how a computational problem may be solved completely without human intervention, provided certain specified conditions are met. Consideration of the example reveals the following important characteristics of computation with a stored program computer:

- (1) The number of different types of instructions that the computer must be capable of executing need not be large.

- (2) The number of instructions in the stored program is extremely small compared to the total number of instructions executed in the running of the program. This is possible because of the unconditional transfer instruction which may be used to provide recycling of a set of instructions.

- (3) The conditional transfer, or test, instruction supplies the necessary means for breaking out of iterative loops at the correct point in the computation.

- (4) The repertory of instructions the computer is capable of executing and the nature of its control unit (i.e., its rules of operation) are distinguishing features of a particular computer.

- (5) The initial contents of the main storage unit, both instructions and numbers, are distinguishing features of a particular computation.

In the preceding description illustrating the operation of a stored program computer, it was assumed that both instructions and numbers were stored in a common storage unit. The reader may ask, then, how the computer can distinguish whether the contents of a particular storage

location represent a number or an instruction, since instructions are represented by numerical codes. The answer is that it cannot. If the control unit is directed to a specified storage location for the next instruction, the contents of that location will be interpreted as an instruction (even though it represents a number). Also, if the control unit is directed to a specified storage location for an operand, the contents of that location will be interpreted as a number (even though it represents an instruction). Such a situation does not, however, imply unavoidable confusion. The treatment of a number as an instruction may be avoided if the control unit is never directed to seek an instruction in a storage location not containing an instruction. The treatment of an instruction as a number may be avoided if the control unit is never directed to transfer to the arithmetic unit the contents of a storage location holding an instruction. However, while at first glance it may seem undesirable, the capability of operating on an instruction as a conventional number is actually an asset and contributes greatly to the utility of a stored program digital computer. This is because as a result of such operations one instruction may be converted to another. By this process, a computer can modify its own program and substitute new sequences of instructions for old ones, when required, during the course of a computation. This feature is valuable as a means of conserving storage.